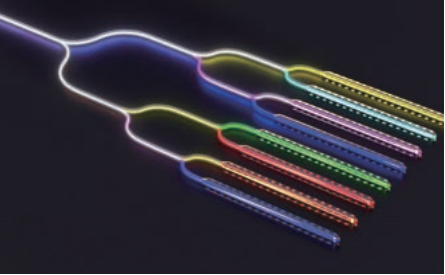

インテルラボ、8波長DFBレーザアレイをシリコンウエハに集積

インテルラボは、シリコンウエハ上に完全に統合された8波長DFBレーザアレイのデモを公開した。この進歩は、インテル社の工場内で既存の製造とプロセス管理により達成され、人工知能(AI)やマシンラーニング(ML)といったネットワーク集約型ワークロード向けの次世代コパッケージド・オプティクスや光コンピューティング・インターコネクトの大量生産を大規模に進める道筋を確保する。

インテル社は、集積フォトニクスへの取り組みの一部である光通信の研究に重点を置いており、シリコンフォトニクス取り組み全体の3つの核心部分が関係している。

これら核心部分は、「光源つまりレーザ、及びそれの変調能力」を含む、とインテルラボPHY Research Labのディレクター兼シニア主席エンジニア、ジェイムス・ジョシー氏(James Jaussi)は言う。「もう1つの重要部分

は、それを増幅し、光信号を検出して受信し、それをCMOSチップ上で電気信号に変換することである。さらに他の重要部分は、CMOSエレクトロニクスである。これは、電気ドメイン内で変調と検出、及び増幅の両方の観点から主にフォトニクスの制御、またはインタフェースに使われる。これらのコンポーネントは、このビジョンのカギであるが、この技術を実際に統合するのは、単一パッケージに集積する能力である」。

原動力:遅延最小化速度の必要性

銅線インターコネクトは、パフォーマンスの壁に当たり続けているため、性能は限界に来ている。同一パッケージにシリコン回路とオプティクスを並べた集積は、エネルギー効率が改善し、伝送距離が拡大した、将来の入力/出力インタフェースとして非常に期待されている。

AIとMLアプリケーションは、銅線インターコネクトではよく起こる遅延欠陥のないスピードを必要とする。波長分割多重(DWDM)技術を利用する最近のコパッケージド・オプティクスソリューションは、帯域幅を拡大し、同時にフォトニックチップの物理サイズを大幅に減らすと見込まれる。しかし、今までは、均一な波長間隔とパワーのDWDM光源の製造は極めて難しかった。

インテル社の取り組みは、光源の一貫した波長分離を確保しながら、均一出力を維持している、つまり光コンピューティングインターコネクトとDWDM通信の必須要件を満たしている。また、光インターコネクトを使用する次世代コンピューティングI/Oによって、高帯域幅のAIとMLワークロードで求められる高度な要求に合わせることが可能である。

この図は、8チャネルハイブリッドIII-V/シリコンDFBレーザアレイを示している。これは、量産ファブ内において多波長レーザ製造能力が飛躍的に伸びていることを示している

(もっと読む場合は出典元へ)

出典元

http://ex-press.jp/wp-content/uploads/2023/03/004-005_wn_laser_arrays.pdf