Quantaイメージセンサ(QIS):すべての光子をカウントする

アバランシェ増倍なしで、室温で単一光子検出感度を示すQIS技術は、回折限界未満のピクセルサイズと、画像再構成における多数の自由度をもたらし、分解能、感度、モーションブラー除去性能を高める。

Quantaイメージセンサ(QIS)と現在呼ばれるものにつながる、イメージセンシングとキャプチャーの新しいパラダイムが提唱されたのは2005年のことである(1)。QISでは、光電子が1個ずつカウントされ、空間と時間の光子数データの組み合わせから、イメージが計算される。

主流のCMOSイメージセンサ(CIS)の3D積層の裏面照射型(BSI:Back Side Illumination)製造プロセスを少し改変した、アバランシェ増倍を利用しないプロセスで実装された、室温の光子計数イメージセンサであるQISは、ジョット(jot)と呼ばれる、フルウェルキャパシティが低い、回折限界未満の特殊なピクセルで構成される。フルウェルキャパシティはわずか数エレクトロンで、0.3e- RMS(Root-Mean Squared、二乗平均平方根)未満という、ディープサブエレクトロンの読み出しノイズ(DSERN:Deep Sub Electron Read Noise)が、アバランシェ増倍を利用することなく達成されている。DSERNは、光電子の有無を表す、QISのバイナリ出力を可能にする。

QISには、数億、あるいは数十億ものジョットが含まれている場合があり、読み出し速度はおそらく1000フレーム毎秒(fps:frames per second)を超え、1テラビット/秒もの生データレートを達成する。QISの積層アーキテクチュアにおいて、高度なノイズ除去アルゴリズムを使用することにより、アプリケーション固有のデータ削減を行うことができ、平均でピクセルあたり1光子未満という極めて低い光量下で、良好なグレースケールイメージを取得することができる。

QISのような光子計数イメージセンサは、CMOSイメージセンサや、その前身である電荷結合素子(CCD:Charge Coupled Device)とは異なる方法でイメージを作成する。これらのデバイスでは、信号の光電荷がセンサ内でアナログ結合され、読み出しにおいて8 ~14ビットの分解能でデジタル変換される。フルウェルキャパシティは、ダイナミックレンジの上限を定め、読み出しノイズ(一般的に1~3e- RMSの範囲)は、下限を定める。モノクロセンサの場合、出力イメージピクセルは、1つのセンサピクセルに集められた電荷のデジタル変換値である。

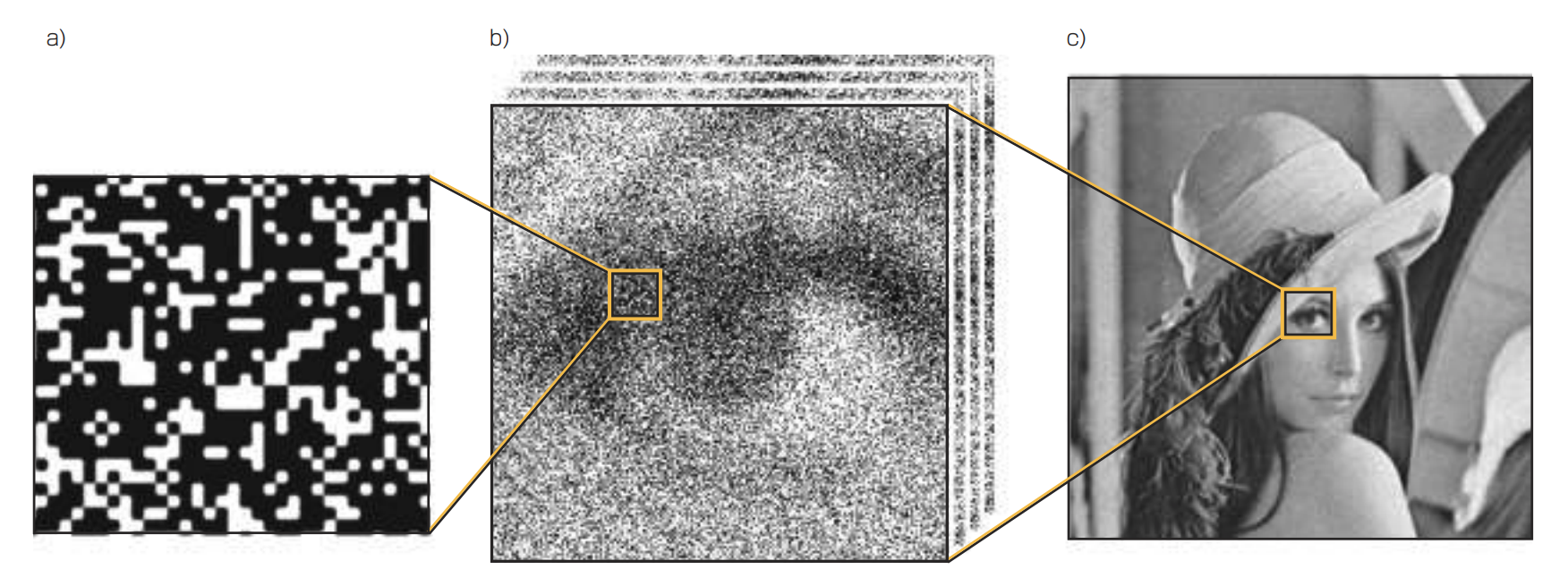

一方、QISなどの光子計数イメージセンサでは、信号がオンチップまたはオフチップでデジタル結合され、ジョット値の時空間キュービクルからイメージピクセルが計算によって形成される(図1)。一度に1つの光子をイメージ化するが(複数ビットのQISによって一度に複数の光子をイメージ化する場合もある)、QISの露光過多に対する本質的な許容度と、複数の高速露光手法を利用して、高いダイナミックレンジ(120dB以上)を達成することができる(2)。ただし、光子計数イメージセンサが高い性能を発揮できないケースが、1つ存在する。それは、多数の光子が同時にピクセルに到達する、フラッシュ撮影時である。

図1 シングルビットQISによるイメージのキャプチャーと計算を示す図。

単一光電子の検出

単一光電子の検出は難しい。電荷が1.6×10-19Cと非常に小さく、電圧が一般的に、読み出し回路のノイズレベルよりも低くなるためである。科学用CMOS(sCMOS:scientific CMOS)を含むCMOSイメージセンサの入力換算読み出しノイズは、一般的に1 ~ 5eRMSの範囲だが、光子計数には一般的に、DSERNレベルが求められる。そこで、ノイズを追加することなく利得を加えることが必要である。

米ダートマス大(Dartmouth College)が考案したQISは、ベースとしてCISプロセスを使用し、ポンプゲートジョット(pump-gate jot)という新しいピクセルデバイス構造を作成するために小さな変更を加えた(3)。この構造は、検出容量が非常に低く、電子あたり数百μVという、他の読み出しノイズ源を十分に克服する変換利得を生成する。この変更以外の面では、BSIや3D積層など、高度に進化したCISプロセスの性質が維持されている。

シングルフォトンアバランシェダイオード(SPAD:Single Photon Avalanche Diode)や電子増倍CCD(EMCCD:Electron Multiplying CCD)検出器など、他のすべての光子計数デバイスは、アバランシェ増倍を利用して、光子検出のための十分な電荷増幅を達成するが、アバランシェ増倍の多数の欠点に対処する必要がある。

アバランシェプロセスは、電荷増幅のばらつきを引き起こす。デバイスの動作に必要な高い電界により、デバイスはシリコン欠陥に非常に敏感になり、ダークカウントレートが高くなり、性能と製造歩留まりが抑制される。デバイスは一般的にバイアス電圧やクロック電圧に非常に敏感で、高い電界は、クロストークや絶縁の必要性から、ピクセルサイズの縮小も難しくする。そのため、アバランシェ増倍を利用するデバイスは、QISよりもピクセル数が多く、分解能が低くなる傾向にある。一般的には、SPADアレイで数十万ピクセル、EMCCDで1メガピクセルとなる。

(もっと読む場合は出典元へ)

出典元

http://ex-press.jp/wp-content/uploads/2019/05/026-029_ft_advances_in_detectors.pdf