シリコンフォトニクス製造アライメントプロセス並行処理の必要性

シリコンフォトニクスデバイスを利益が出るように量産するには、自動サブシステムは、ウエハレベルのデバイス評価から最終アセンブリおよびパッケージングまでのステップをサポートするアライメントプロセスを必要とする 。

1997〜2002年のテレコム主導のフォトニクスブームが突然終わるよりもかなり前の2000年に「フォトノミクス」(photonomics)という用語が作られ、業界の経済的安泰のために工程自動化の重要性が強調された。そこで提示された経済的な例、ワークステーションあたり1時間に60パーツは、今日では古くさいようである。今日のシリコンフォトニクス製造プロセスとそれとを比較する。シリコンフォトニクス製造では、ウエハあたり数千のデバイスが造られる。1時間に60パーツのペースは、20年前なら非常に速かったかもしれないが、今では、現在そして今後の競争的状況では持続不可能を意味する。

テレコムブームの終焉以来、業界は復活した。その原動力となったのは、ストリーミングビデオ、オンラインミュージック、スマートフォンやクラウドコンピューティングである。フォトニクス産業とその新たなパートナー、半導体製造にとって好材料は、潜在性が無限であるように見えることだ。悪材料は、これらの新しいデバイスは、前例のない数量で効率的に製造されなければならないこと、歴史的に短い時間枠でコストカーブ急降下に追随しなければならないことである。

この新しい環境で成功する決め手は、2000年からの古い教訓、自動化、特に結合最適化ステップは、ウエハから最終アセンブリまで、非常に多くの試験とパッケージング動作にとって基本であるということだ。とはいえ、今日では、2000年と比べて違った種類の自動化が必要とされている。今日のデバイスはもっと小さく、一段と複雑であるので、その挙動はもっと難しくなっており、試験とパッケージングを必要とするものが多くなっている。

斬新なデバイス、新たな課題

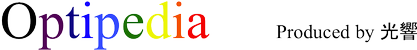

まず、以前のシングルモード結合の明確で予測可能なガウシアンは、もはや既定事実ではない。それどころか、シリコンフォトニクス結合は、中央周囲多数の局所最適と鞍点により複雑なプロファイルとなり、疑似ガウシアンピークにすぎない。これは、デバイスがウエハ上にある時のデバイスのプロービングから分離されたチップや補助デバイスのパッケージングやテストステップまでのことである。1990年代に登場した比較的単純なアライメントエンジンと比べて、明らかに、異なる最適化戦略が必要である(図1)。

もっと複雑な結合以外に、デバイスあたりの結合がもっと多くなる傾向がある。シリコンフォトニクスデバイスは、入出力だけでなく、多くのチャネルを実装できる。こうしたデバイスの短尺導波路では入出力が相互作用することがよくあり、広範囲のアライメントは動く標的になる。

以前のアライメント自動化技術であれば、これは決定に時間がかかる連続アライメントループである。これの次はあれをアライメントし、元に戻ってデバイス全体で繰り返し、個々の連続アライメントの先行のものへの影響を取り消す、さらにもしドリフトが発生するとその操作を何度も何度も行うことになる。これらのアライメントの多くは、その上、角度の影響を受けるので、自由度の至る所で、また入出力とチャネル全体で多重最適化が必要になる。

2015年、こうした課題に応えるために、PI社は、マルチ入力、マルチ出力、マルチ自由度にわたって1度に、並行的にアライメントできることを実証した。これにより、デバイスとそのチャネル全体で行きつ戻りつする一連の連続アライメントループがなくなった。それどころか、グローバルコンセンサスアライメント(必要なら、トラッキングも含めて)は、高速ワンステップで完了する。

このアライメントステップだけで、少なくともアライメントステップに関しては、スループットは1時間に60デバイスから2ケタ増やすことができる。連続アライメントの繰り返しループをなくすことによる、数ケタのプロセススループット改善は、ただちに達成可能である。このことは、アライメントがデバイス製造全体の調整項目でなくなることを意味する。

図1 シリコンフォトニクス結合は、明確な予測可能ガウシアン結合横断面から外れることがよくある。この種のプロファイルは、従来のアライメントアルゴリズムで確実に最適化することはできない。さもなければ、その最適化は、広範囲の最適点ではなく、局所最適点の一つにロックする危険を冒すことになる。これは、標的領域のエリアスキャンを行うことで効率よく達成可能であり、それによってその全体にわたる結合横断面をマッピングできる。ピエゾベースのスキャナは、1秒の小数点以下の時間でこれを達成できる。(提供:PI社)

並行処理:プロセス経済の決め手

フォトノミクスにとってのこのことの重要性は理解しがたいが、この並行処理は、生産チェーンにおける多重ノードでプロセス経済学を実現するものである。つまり、まだウエハ上にある時にデバイスの機能確認から、各アセンブリステップを実施する、そのすべてのステップでデバイスの健全性を検証するまでである。これによって不良な製品、つまり破損品が確実に、さらにコストのかかるパッケージングステップを通過しないようになる(図2)。

パラレル最適化機能は、古典的デジタル傾斜サーチの新しい改良に基づいているが、パラレル最適化のほかに、まずファーストライト(所望の性能達成を確認する観測)を実現する必要があり、次に各結合の主モードを局所化して疑似的ロックオンから守る必要がある。そうでなければ、最適化は、グローバル最適化ではなく局所最適化の一つにロックオンするリスクがある。

この最適化は、ターゲット領域のエリアスキャンを行うことで効率よく達成できる。これによって、全域にわたり結合横断面をマッピングできる。これは、以前はソフトウエアで行われ、完了までにかなりの時間がかかった。理由は、従来のラスタスキャンや蛇行スキャンでは、通信待ち時間と各スキャンラインの端で決定に時間がかかること、この両方である。悪いことに、ほとんどのアプローチはポイントごとに動いて取得するシーケンスに基づいており、スキャンの各データポイントで時間のかかる決定と通信待ち時間が増える。

ソフトウエア最適化プロセスはすべて、2つのイノベーションによって古くなった。まず、完全ファームウエアベースのコマンドは、内的な位置、つまり波形と同期データ取得を利用する。次に、単一周波数正弦波、つまりスパイラルスキャンである。これは、ファイバやピンセットのような機械的要素における刺激的な構造共鳴を回避しながら、滑らかに連続的に進む。結果は、プロセススループットにおけるけた違いの改善である(図3)。

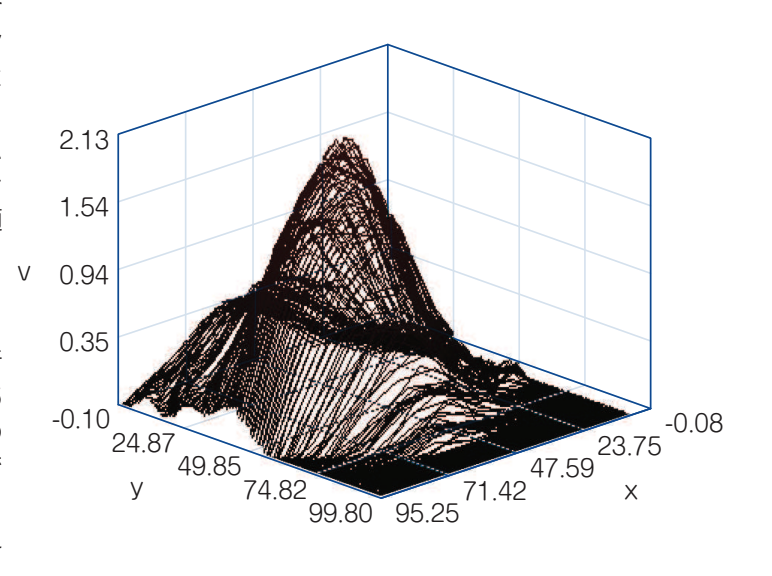

図2 高速18軸並行フォトニクスアライメントシステムは、2つの6自由度ナノマニピュレータと2つの高速ピエゾXYZスキャナをベースにしており、これは導波路デバイスの両面ウエハプロービング向けである。これは完全デジタルのクローズドループであり、実装されているのは、排他ゾーン機能、内部データ記録、ナノスケール安定位置保持、およびファームウエアベースの高速スキャニング、モデリングとマルチチャネルN×M傾斜サーチ機能である。アプリケーションビデオは、https://youtu.be/X7zkUWo-lI8で見ることができる。(提供:PI社)

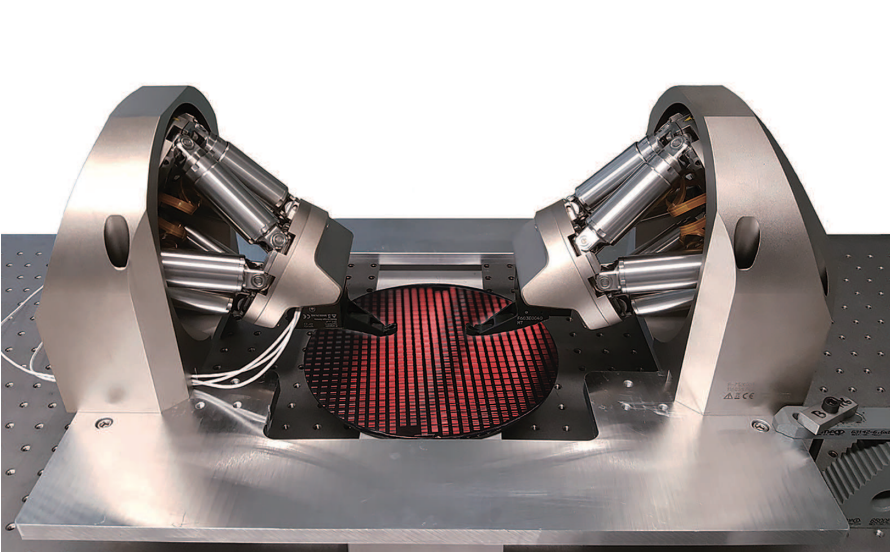

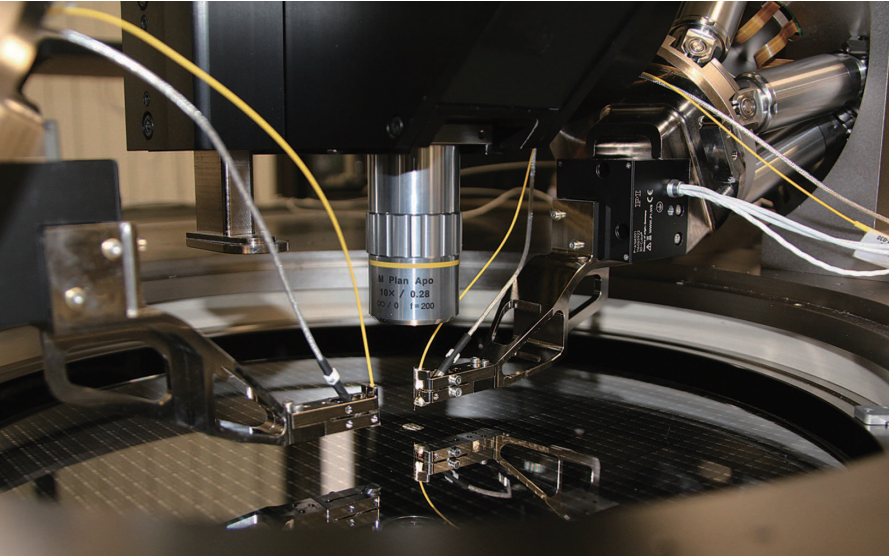

図3 Cascade MicrotechのCM300xiフォトニクス対応エンジニアリングウエハプローブステーションには、PI社のFast Multichannel Photonics Alignment (FMPA)システムが組み込まれている。目的は、オンウエハシリコンフォトニクスデバイスの高スループット、ウエハの安全、ナノ精度光プロービングである。6軸ヘクサボッド(6支柱)位置決め(上段左)とピエゾXYZスキャナ(ヘクサボッドにマウントされた黒いキューブ)の両方とも、並行運動をベースにしており、狙いは動力学と精度の改善である。(提供:Cascade Microtech、FormFactor子会社)

(もっと読む場合は出典元へ)

出典元

https://ex-press.jp/wp-content/uploads/2018/01/ft2_positioning.pdf