製造可能な全領域を探る集積フォトニクス設計アプローチ

望ましい機能性だけを知るだけで、「オブジェクトファースト」ソフトウエアは、より小さな最適化されたシリコンフォトニクスデバイスを設計する。

デジタル回路の設計は現在、ヴェリログ(Verilog)やVHSICハードウエア記述言語(VHDL)など、ハードウエア記述言語が優勢である。回路設計のこのような自動化により、最近の数十億トランジスタのコンピュータプロセッサの開発が可能になった。

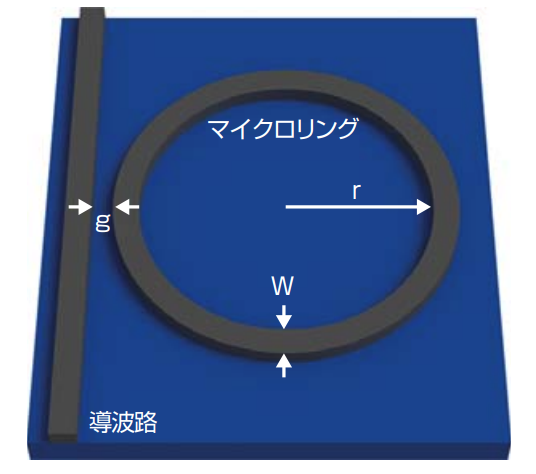

一方、集積フォトニクスデバイスは、まだ手動で設計されている。設計者はまず、少数(2~6)の自由パラメータを持つ解析理論に基づいて基本設計を選ぶ。基準的な例は、狭スペクトルフィルタとして一般に利用されているマイクロリング共振器(図1)であろう。設計は単純であり、調整可能パラメータは、リングの半径(r)、導波路幅(w)、それにリングと導波路間のギャップ(g)のわずか数点にすぎない。設計者は次に光学シミュレーションを何度も走らせてこれらを調整する。この力づくのアプローチは非効率であり、設計者は既知のデバイスの小さなライブラリに制約される。

図 1 集積フォトニクスで一般に使われるマイクロリング共振器の概略図。この共振器は、閉じたリング内に形成された導波路と入/出導波路で構成されている。リングは共振器キャビティとして機能する。主な設計パラメータは、リングの半径(r)、導波路幅(w)、それにリングと導波路間のギャップ(g)。

任意のフォトニックデバイス

しかし、製造可能なデバイスの全域を探ることができたらどうだろう。もしこれに成功すれば、デバイスパフォーマンスの改善、デバイスサイズの縮小が保証されることになる。残念ながら、製造可能なデバイスの領域は絶対的に膨大である。例えば、1×1μmデザイン領域でシリコンフォトニクスデバイスの設計をしたいと考える。それを0.1×0.1μmピクセルに分割するなら、最近のナノファブリケーションで簡単

に達成可能であり、各ピクセルはシリコン(1)を含むか、あるいは含まないか(0)のいずれかが可能であるので、可能なデバイスは2100㲔1030得られる。

この例から、完全自由設計について2つの重要な洞察が引き出せる。まず、完全自由設計は自動化が不可欠である。設計者が人間だったら、デバイスのパフォーマンスは規定できるだろうが、実際の設計はコンピュータアルゴリズムで行われなければならない。二番目に、すべての可能なデバイスを単純に力づくで探すことは解決困難で、もっと効率的な設計法が必要である。

理想的には、計算コストが設計の自由パラメータの数に関係しない最適アルゴリズムがほしい。ありがたいことに、そのような最適化方法が存在することが分かった。関連のある方法は、航空宇宙設計、機械学習など他の分野で以前から使われていたが、光学設計に導入されたのはつい最近のことである。

設計アルゴリズム

われわれの研究グループは、任意のフォトニックデバイスの設計に2つの方法を用いる。まず、いわゆるオブジェクトファースト設計法(1)を用いて構造について最初の推測を行う。この方法では最初、電磁場は非物理的でよいが、考えられるどんなパフォーマンス制約でも満たすようにする。構造と電磁場の両方を変更することでマクスウェル方程式違反の減少を繰り返す。マクスウェルの方程式に対してわれわれのパフォーマンス目標が優先であるので、われわれはこの方法を「オブジェクトファースト」と呼んでいる。

(もっと読む場合は出典元へ)

出典元

https://ex-press.jp/wp-content/uploads/2016/07/LFWJ1605_P18-19_ft01.pdf