CMOSとCCD統合によりNIR TOFオンチップイメージャを実現

全電荷ハンドリング容量と低雑音動作を維持しながら、モノリシックCCDシステム・オン・チップ技術は、今ではCMOS環境に組み込まれている。そこでは、背面照射と厚くなったディテクタボリュームによって、感度はけた違いに向上している。

過去数十年、イメージングの世界ではCCD(電荷結合素子)とCMOS(金属酸化膜半導体)技術との比較で多くの文献が著されている。どちらかのアプローチの優位性についての激しい議論や熾烈な論争さえも当たり前になっている。

こうした対立に応えてESPROSフォトニクス社は、厚い基板を持つ背面照射イメージャを開発した。このイメージャは、近赤外(NIR)光パフォーマンスを改善しながら、CCDとCMOS技術を統合している。この真のシステム・オン・チップ(SoC)飛行時間(TOF)イメージャにより、改善された時間遅延イメージング(TDI)や蛍光寿命イメージング(FLIM)という成果が可能になる(外観写真参照)。

ESPROSフォトニクス社のepc610モノリシックCCDCMOS飛行時間背面照射イメージャは、時間差イメージング(TDI)や蛍光寿命イメージング(FLIM)におけるNIR光パフォーマンスを改善する。

従来の問題点

市販のCMOSイメージセンサ(CIS)モジュールをみても、標準CMOSプロセスはNIR照射の検出にあまり適していないと言える。これは、一部にはピンド・フォトダイオード(PPD)の感受性領域の厚さが数μmしかないためである。これは光の吸収長(シリコンでは850nmの光で約13μm:図1)よりもはるかに少ない。

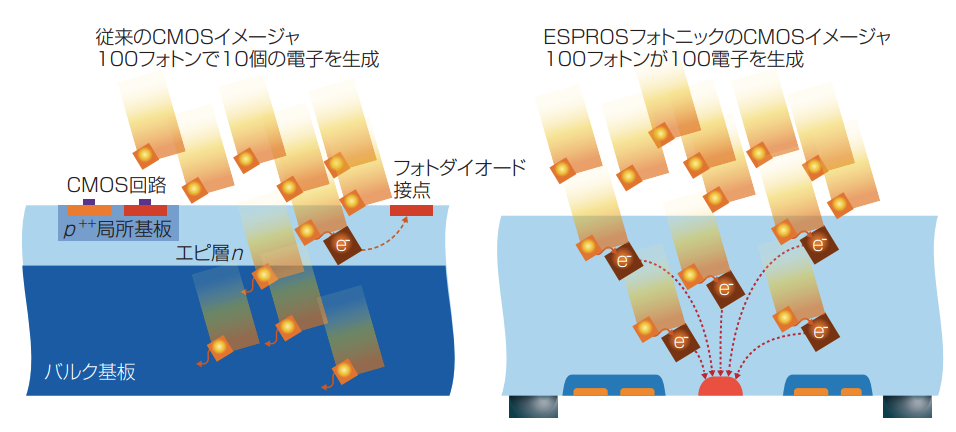

基板材料で光の吸収長、空乏域の厚さ(さらに、下の追加拡散領域)、表面の反射特性が組み合わさり、所定の波長でイメージャの量子効率(QE)が規定される。

標準フォトディテクタでこれらのパラメータの最適化は、CMOSもしくはCCD製造工程による境界条件の制限を受ける。例えば、空乏域は商用プロセスで利用できるエピタキシャルの厚さに制限され、一方光反射特性はバックエンド(BEOL)スタックに規定される。つまり、干渉縞により、BEOLスタックは波長に対してQEの支配的な変動要因となる。

しかし、CMOSとCCD特性を統合する同社の新しい混合プロセスは、これらの制限に対処している。特に、適切な基板材料の選択が、厚さ50μmの完全空乏ディテクタに寄与する。この結果、波長850nmで>80% QEと波長950nmで>50%を維持しながら、NIR領域における優れたQEが得られる(図2)。

図1 従来のCMOSイメージは、100の入射フォトンあたり10個の電子を生成する。しかし、ESPROSのハイブリッドCCDCMOSイメージャは、ほぼ1対1の比であり、100の入射フォトンに対して最大90個の電子が生成される。

図2 の標準CMOSまたはCCD設計と比べて、ハイブリッドCCD-CMOSアーキテクチュアは、近赤外領域のイメージャで、量子効率の大幅改善となっている。

CCD-CMOS統合

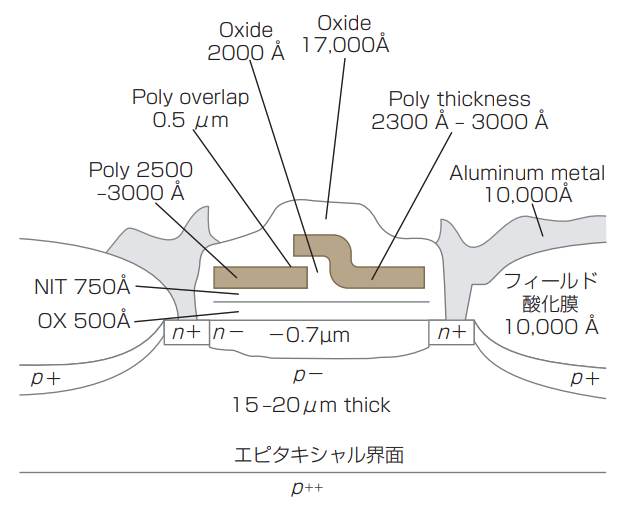

標準CMOSプロセスで効率のよいCCDを実現するには、デュアルポリシリコンアプローチで良好な電荷移動効率(CTE)を達成する必要がある。CCDゲートは、1つのポリ層から他のポリ層にオーバーラップしており、非常に薄い酸化被膜で分離されているだけである。薄く、よくコントロールされたポリ層が高CTEの決め手になる(図3)。

しかし0.25μm以下のサイズを使うことで、デュアルポリはもはや可能ではなくなる。180nm以下で始まるプロセスノードがBEOLで化学機械研磨(CMP)を使用するからである。CMPは、層堆積と構造化で確実にフラットな表面を必要とする。したがって、2番目のポリシリコン層はもはや可能ではなくなる。良好なCTEの決め手は、2つのゲート間の非常に狭いポリギャップである。そのようなナローギャップは、45nm(それ以下)のプロセスを使うことで簡単に達成できる。しかし、そのような技術ノードの開発および装置コストは法外に高価であるので、CMOSへのCCD導入の候補としては、それは除外される。ESPROSの技術は、新設計の製造工程によってこのジレンマに取り組む。この新しい製造プロセスにより、100nm以下のポリゲートが、標準の180nmプロセス環境でも可能になる。

50μm完全空乏シリコンディテクタボリュームは、この混合プロセスによるイメージャの感度で大きな要因の1つをなす。その深さが、標準的なCMOSプロセスで薄いエピタキシャル層を透過するだけのフォトンをバルク基板で吸収できるようにするからである。ここでは、フォトンは無駄なエネルギーを熱として生成する。もちろん、そのように厚いディテクタボリュームでは、電子-ホールペアを分離してCCDゲート下の電子を収集するには、十分に高い電界が必要になる。

さらに、標準的なCMOSフロントサイドイメージャでは、トランジスタがチップ前面の光路に置かれている。これらのトランジスタは、入射フォトンによる活性化から保護されなければならない。しかし、これらのトランジスタをブロックする不要な効果は、光の収集に利用する表面積を大幅に減らすことにもなる。それに対して、この新しい混合プロセス環境では、トランジスタが存在しないイメージャの背面を使って光を収集する。この背面照射で達成される100%のフィルファクタと50μm厚ディテクタボリュームQEゲインとを結びつけることにより、標準的なCMOSに対してけた違いの感度向上が可能となった。

イメージャは背面照射(BSI)であるので、しっかりと調整された反射防止(AR)膜を適用することで、所望の波長範囲でディテクタの反射を低減できる。また、背面の入光ウインドウは破壊的な酸化物スタックがない完全フラットであるので、標準的なウエハレベルプロセスを用いて屈折率フィルタを堆積することができる。

この製法により、ディテクタの背面に狭帯域のフィルタバンクをつけることが可能になり、様々なモバイルアプリケーション向けの超小型分光計が実現可能になる。この新しいアプローチは、入射ウインドウの金属スタックを削除して、改善された光学デザイン向けに大きな入射角とすることができるので好都合でもある。

図3 デュアルポリCCD。電荷移動は、左(直線)と右(オーバーラップ)のポリゲートで起こる。2つのゲートがオーバーラップしているので、Nウエルにおける仮想バケットの横方向分離は実質的にゼロである(情報源:ジェイムス R.ジェインシック、Scientific Charge Coupled Devices,SPIE Press)。

(もっと読む場合は出典元へ)

出典元

https://ex-press.jp/wp-content/uploads/2015/11/LFWJ1511_p26-31.pdf