現実の要求に応えて進化するシリコンフォトニクス

目指すものは変わらない。フォトニクスとエレクトロニクスを集積してコスト削減、データリンクパフォーマンス向上が目標。しかし、開発者は、化合物半導体光源を受け入れ、シリコンに貼り付けるか、チップに外付けするかする。

シリコンフォトニクスは、実験室から出て現実世界の技術になりながら進化を続けている。基本的な目的は同じままであり、光と電気のコンポーネントをシリコンベースのプラットフォームに集積してローコストで大容量伝送を実現することである。しかし、開発者は技術を改良して、シリコン固有の性能限界を回避し、進展するアプリケーション要求に応えようとしている。

技術的代替案を検討する時期にきており、同様にまずは標準の開発努力を行い、さらには将来のニーズにどのように応えるかを考える時である。電気ポンプのシリコンエミッタは、まだ実現しそうにないので、基本的な選択肢の1つは、外部光源からの光を使うか、III-V 属のエミッタをシリコンに貼り付けるかになる。他には、デバイスの設計、製造技術が含まれる。また、シリコンの機能と調和する伝送プロトコルは、伝送プロトコルの選択に適合するユーザの要求があるので、シリコンの機能とユーザシステムの仕様との調和がとれていなければならない。

進化の原動力

シリコンフォトニクスの背後にある原動力は、コンピュータパワーとデジタルデータ伝送の力強い成長である。今日の主要なニーズは、ハイパフォーマンスコンピュータ(HPC)のバックプレーン接続やデータセンタ内の伝送である。

計算処理能力は数年前に、1 つの重要な性能限界に達した。処理コアは、能動冷却なしには、1 秒間に数十億動作を超えるパフォーマンスが出せない。このため、設計者はマルチコアチップにシフトし、ますます並列動作が増えている。これはパーソナルコンピュータでさえも同じことだ。HPCは、システム内のバックプレーン間で膨大なデータの移動があるので超並列処理を必要としている。クラウドコンピューティングに使用されるデータセンタやサーバファームも同様に、多数のマシーン間で高速データ転送の要求が膨大になっている(1)。

米国のIBM ワトソンリサーチセンタ、シリコンナノフォトニクスプロジェクト担当マネージャ、ユリイ・ウラソフ氏(Yurii Vlasov)によると、新しいデータセンタ標準が開発されつつある。これはチャネルあたりシリアルレート25Gb/sとなる。少なくとも今後5年は、シリコン技術のラインレートはこれ以上高くなりそうにない。「だから、チャネルあたりの伝送容量を増やすことは重要ではない。必要なことは、チャネル数、波長多重レベルの拡張が示せること。したがって、チャネルあたりのファイバが少なくてすむようになる。必要としているのは、より高密度な集積化ができる技術だ」と同氏は説明している。

データセンタでは非常に多くの接続がコストを危機状態にしている。最も重要なことは「ソリューションの総コストだ」とウラソフ氏は言う。これには、モジュール、電気から光フォーマットへの信号変換と逆の変換、さらにケーブルが含まれる。ケーブルが総コストの多くの部分を占めるようになる、数10 メートルより長い距離では、WDM(波長分割多重)や他の技術を使用して各ファイバに、より多くのチャネルを詰め込むことが一段と重要になる。

100Gb/sイーサネットへの拡張

IBMは、25Gb/sシリコン光モジュールを基本的な構成要素と見ている。目的は、シングルモードファイバで100Gb/s、それ以上を多チャネル並列伝送する新しい世代のファイバシステムだ。初期の100Gb/sイーサネットは、各10Gb/s を10本のマルチモードファイバで短距離伝送した。波長は850 nm。新しいIEEE.802.3bm提案はチャネルあたり25Gb/s 伝送となっており、4波長は1310nm帯で20nm間隔、伝送距離はシングルモードファイバで500m。

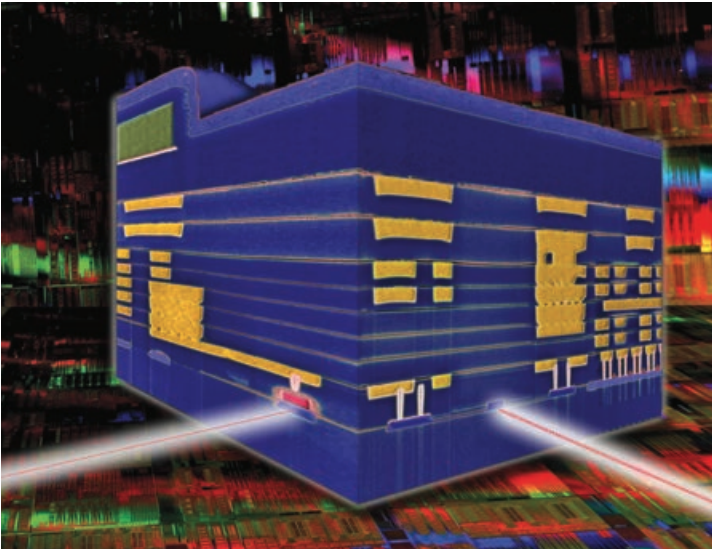

2012年12月のIEEE国際電子デバイス会議:International Electron Devices Meeting(IEDM )でIBM は、90nmCMOS 技術を用いた初めてのモジュール製造について報告した(2)。モジュールは、1500-1550nm 帯で850GHz チャネル間隔、4チャネルコースWDM(CWDM)で、フィルタはフラットトップ500GHz。ディテクションはゲルマニウムフォトダイオードを用いており、これはCMOSプロセスに対応、3dB 入力帯域20GHz 以上、トランスインピーダンスアンプリファイア(TI A)、リミッティングアンプ( LA )、出力バッファを持つ。

「レーザ以外の全機能がチップ上にあるので、光パワー供給ということになる」とウラソフ氏は言う。入力信号はゲルマニウムフォトダイオードでモジュールに結合し、外部の連続波レーザが「光パワー供給」であり、変調器を介して送信器に結合している(図1)。また、モジュールにはWDM フィルタ、導波路、クロッシング、方向性カプラ、垂直グレーティングカプラが含まれる。

数十億ドル投資したシリコン技術から受ける恩恵の他に、ウラソフ氏によると、IBM のアプローチは2 つの要素からの恩恵をうける。シングルダイを使うことで標準のピック&プレイスアセンブリ技術が可能になりパッケージングコストが大幅に削減できる。この設計は、標準のマイクロエレクトロ技術にも対応しており、コストがかかるパッケージングが終了する前、アセンブリ中にコンポーネントのテストができる。

ウラソフ氏は、400ギガビットイーサネット(GbE)に期待しながら、チャネル間隔をさらに詰めて25Gb/s 16チャネル伝送を考えているが、動作温度はまだ0℃~70℃の範囲で大きなクロストークがないという段階。同氏によると、100Gb/sから400Gb/sへの拡張は、技術問題というよりも設計の問題である。

図1 90nm技術で製造したIBM シリコンナノフォトニックチップの拡大図。キューブの左側の赤色部分がシリコン上に作製したゲルマニウムディテクタビームが入っていく右の青い面が変調器。黄色のエリアは導体。右下の小さな赤いドットはシリコントランジスタ( IBM 提供)。

(もっと読む場合は出典元へ)

出典元

https://ex-press.jp/wp-content/uploads/2014/02/0038pf.pdf