シリコンチップの欠陥を画像化するテラヘルツ反射率測定

テラヘルツ顕微撮像法はシリコンチップの反射率測定による欠陥位置の測定精度がサブミクロンレベルに向上する。

集積回路(IC)技術の複雑性の着実な増加、例えば3Dスルービア(3D‐TSV)技術の登場は、利用可能な検査や欠陥分析装置の性能を限界にまで追い詰めている(1)。非破壊試験法のなかで、時間領域反射率測定(TDR)は、電子パッケージの故障を例外的な高速度で検出できると考えられている。今日の「閉ループレーダ」とも呼ばれるTDR システムの多くは、全電子式を採用し、ステップまたはパルス発生器と広帯域オシロスコープを主要な部品として使用している(2)。電磁信号は高周波ケーブルとプローブチップを通して試験デバイス(DUT)に伝送される。DUT内の伝送経路の不連続性は注入されて反射する信号の一部になる。これらの反射を時間領域で監視すると、構造欠陥の検出と欠陥構造の識別が可能になる。

TDR システムの空間分解能dmin には注入信号の立ち上がり時間と次式の関係がある。

ここで、cは光速、εr,dff は伝送線の相対有効誘電率を示している。τrise=11.1psの速い値を測定したときの全電子システムは約dmin=365μm(εr,dff=5)の分解能しか得られない。この限界を突破して小スケールのチップレベル構造や先進型パッケージの検査を可能にするには、全電子式から超高速オプトエレクトロニクス技術への切替えが必要になる。

最近、欠陥検査用の高速フェムト秒レーザ駆動オプトエレクトロニックTDRシステムが米インテル社から商品化された(4)。このシステムを使うと、全電子システムを上回るτrise=5.7psという大きな改善が可能になる。しかしながら、このシステムの主要なボトルネックはオプトエレクトロニックサブピコ秒領域のスイッチング速度の利点を十分に利用できないことであり、オプトエレクトロニックパルス発生器/検出器デバイスとDUTとの間の信号伝送には導波路とプローブ部品の使用が必要になる。これらの部品は110GHz 以上の周波数を伝送できないため、解像力の大部分はTDRシステムの内部で失われる。

われわれが最近実証したように、現在、このボトルネックは新しい微細加工プローブチップを適用し、DUTの直前で広帯域光伝導(PC)パルス発生と検出を行なうことで、効果的に排除されている(5)。この先進型オプトエレクトロニックシステムを使用して、τrise=1.1ps の前例のない信号の立ち上がり時間が達成された。初期の配置とは違って、このプローブはプローブ/導波路容量結合による無接触モードでも使用できる。このモードは単一時間領域の解析とは異なり、疑わしい領域の空間時間分解場マッピングにより強化された欠陥局在化にも適用できるため、標準のTDR システムの重要な拡張になると考えることができる。

測定システム

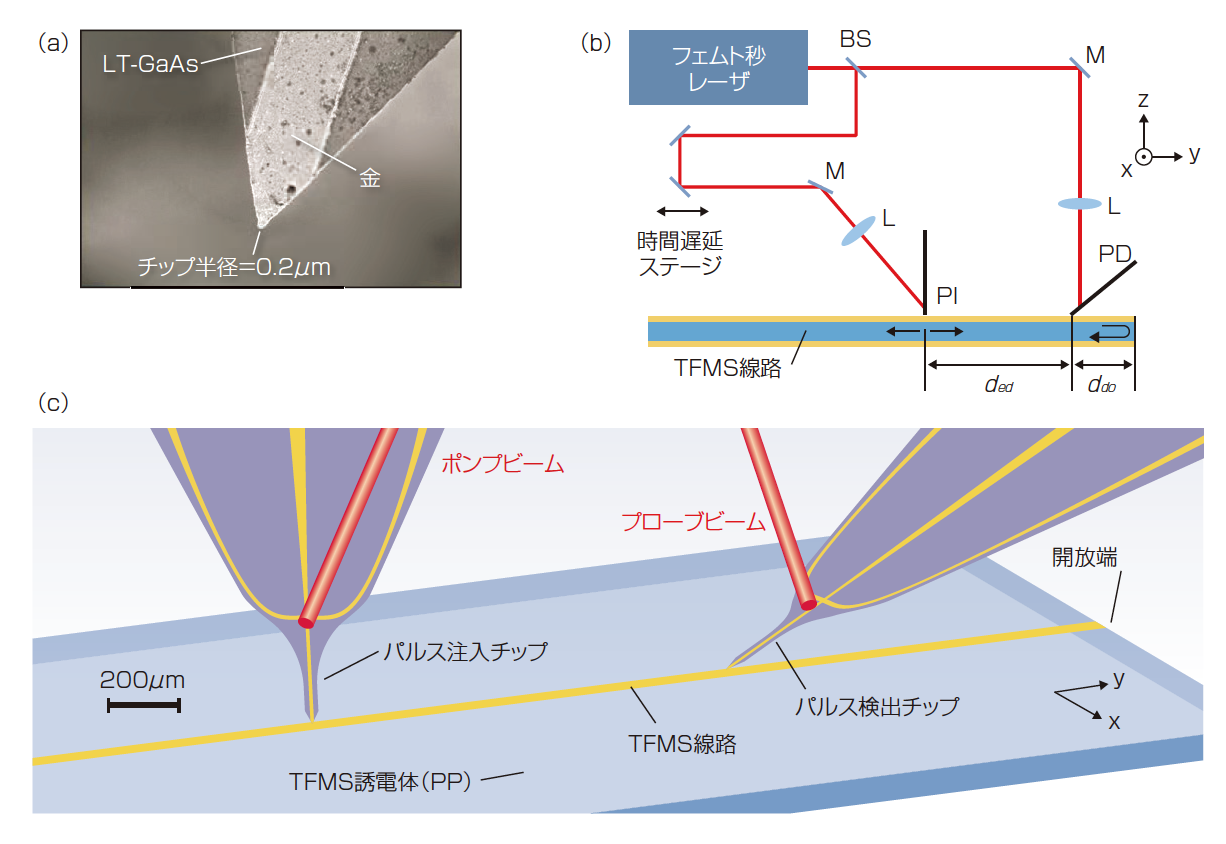

TDRによる欠陥孤立化のシステム能力を実証するために、テラヘルツ領域において既知の透過特性をもつ薄膜マイクロストリップ線路(TFMS)がDUTとして使用された(6)。このオプトエレクトロニック実証システムは時間領域測定用の伝統的なポンプ/ プロブ装置にもとづいている(図1)。主要部品は780nmの波長、150fsの半値全幅(FWHM)パルス幅および78MHzの繰返し速度をもつTi:サファイアフェムト秒レーザと二つの微加工した同じPC プローブチップからなる。レーザの出力ビームはビームスプリッタ(BS)を使用して、それぞれが4mW の平均パワーをもつポンプビームとプローブビームに分割される。

図1 (a)はプローブチップの走査型電子顕微鏡写真、(b)はテラヘルツ時間領域測定に使用する光ポンププローブ装置の概念図、(c)は測定に使用するプローブの構成と配置の拡大図を示している。

(もっと読む場合は出典元へ)

出典元

https://ex-press.jp/wp-content/uploads/2012/01/201201_0030feature03.pdf