プレーナアーキテクチャによって最適化されたSi単一光子計数検出器

シリコンシングルフォトンカウンティング(単一光子計数)検出器の新しいプレーナ構造は、ピコ秒のタイミング分解能、低い暗計数率、低い電力消費量を維持しながら、検出器の効率を2倍に高める。

Laser Focus World誌の2005年4月号に、伊オプトエレクトロニック・コンポーネンツ社(OEC;OptoElectronic Components)とそのグループは、伊マイクロフォトンデバイシス社(MPD)からのカスタムプレーナプロセスに基づくCMOS対応の単一光子計数検出器の開発を報告した。このタイプの検出器はピコ秒のタイミング分解能と低消費電力を提供し、それゆえ非常に頑強となり、高速のタイミング分解能を必要とする用途に適している。しかし、高抵抗率の「厚い」シリコンと専用プロセスを使った光子計数検出器と比較して、プレーナ光子計数検出器は特に近赤外領域において検出効率が低い。

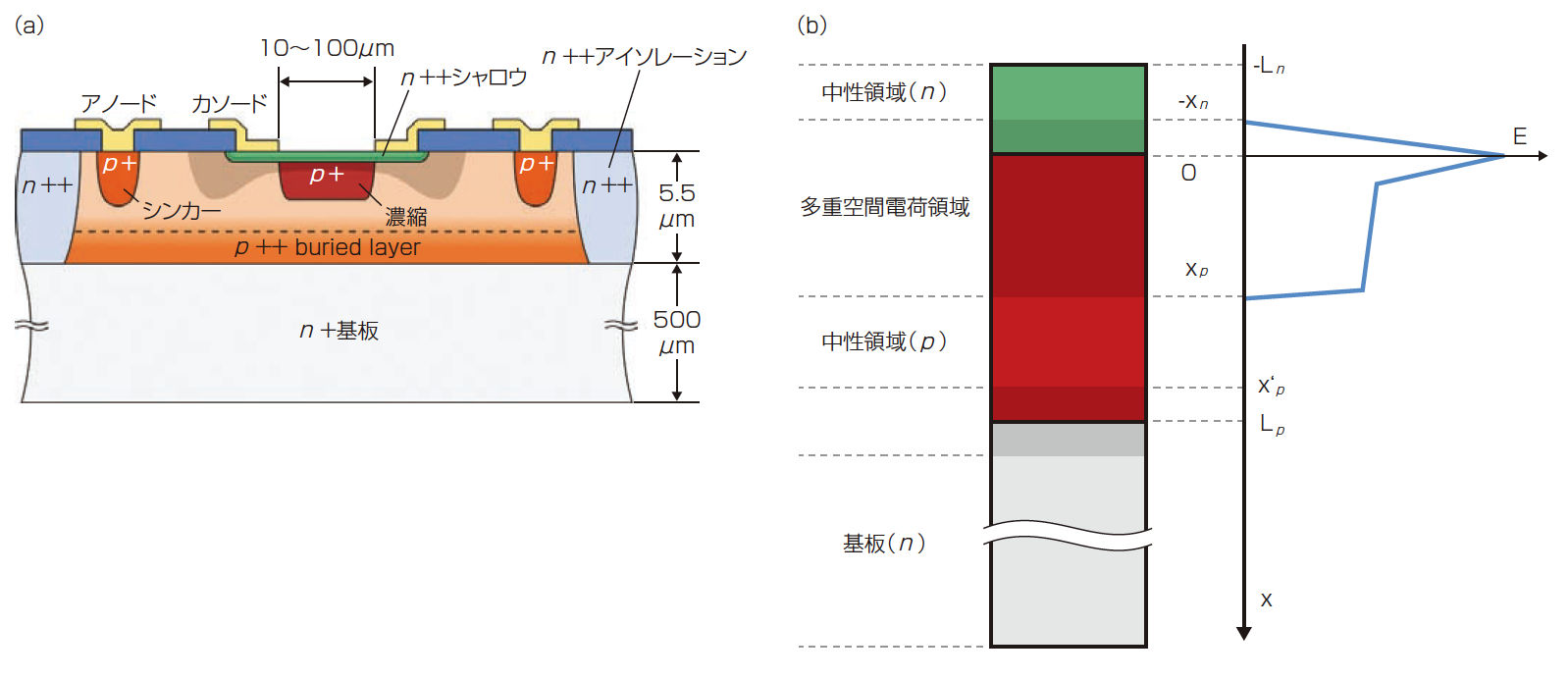

「厚い」リーチスルー構造は非常に高い検出効率(一般に650nmで75%)を提供するが、高いバイアス電圧(400〜600V)を必要とし、たった300〜800ps台のタイミング解像度しか達成できない。それに代わって、われわれの2005年プレーナ構造は30ps以下のタイミング分解能を提供し、非常に低いバイアスで動作する(それゆえ、非常に頑強になる)。しかし、検出効率は650nm領域で2.5分の1であった。25年前からこれらのデバイスの研究を続けている単一光子アバランシェダイオード(SPAD)と光子計数エレクトロニクスの分野の先駆者である伊ミラノ工科大学(Politecnicodi Milano)のセルジオ・コバ氏(Sergio Cova)の努力によって、今や同氏のチームはピコ秒のタイミング分解能、低い暗計数率、低い消費電力を維持しながら、検出器効率の倍加に導く新しいプレーナ構造を設計した(1)〜(3)。

検出機構

標準的な単一光子検出器を仮定した場合、光子検出効率(PDE)はデバイスのアクティブ領域に入射した光子が効率良く検出される確率として定義される。アクティブ領域に光子が吸収され、その結果として生成された電子または正孔が高電場領域に到達してアバランシェを引き起こすことが必須である。

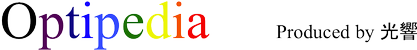

したがって、PDEは光子吸収とアバランシェ開始の両効率の組み合わせになる。検出プロセスのより深い理解を得るために、プレーナ検出構造が単純な一次元表現で可視化し、4つの異なる領域、つまり基板、多重空間電荷領域、空間電荷層を挟む二つの中性領域に区分した(図1)。

デバイスへの入射に成功した光子は4層のうちの1 層にその吸収係数に依存する確率で吸収される。光子が空間電荷領域に吸収されたとすると、光生成された1対のキャリアは瞬時に分離され、電場によって加速される。しかし、衝突イオン化過程はランダムであるため、これが自立したアバランシェを引き起こす保証はない。

光子が下部中性領域(p型)に吸収されると、光生成された正孔は他の多数キャリアによって熱化される一方、電子は強電場が存在しないためその領域内をランダムに拡散する。そのランダムウォーク中に、電子は正孔と再結合するか、基板に到達する。いずれの場合にも電子はこの領域から失われるため、アバランシェを誘起することはない。

反対に、電子が多重空間電荷領域に達した場合には、それはより強い電場ゾーンに向けて加速され、アバランシェを引き起こすことが可能になる。したがって、下部中性領域に吸収された光子が検出される確率は、電子が空間電荷領域に達する確率、いわゆる電子収集効率とトリガリング効率の積になる。

同様な状況は、光子が上部中性領域(n型)に吸収された場合にも起きる。唯一つ違うことは、この場合の少数キャリアは電子ではなく正孔であり、それは中性領域体積内または二酸化ケイ素との界面で電子と再結合すると消失するということだ。

最後に、光子が基板(n型)に吸収された場合、少数正孔は活性領域内でアバランシェを開始する方法を全く持ち合わせないため、光子が検出されることはない。

図1 典型的な薄い2重エピタキシャル単一光子アバランシェダイオード(SPAD)の垂直断面と(a)、多重空間電荷領域の定性的電場プロファイルを含む薄いSPAD のアクティブ領域の断面(b)が対照されている。(全画像提供;ミラノ工科大学)(3)

新しいプレーナプロセス

ミラノ工科大学のチームは、100psより良いタイミング分解能を損ねることなく、550nm以上の波長で高いPDE、すなわち650nmで60%と800nmで40%を持つデバイスの開発に成功した(図2)。このプロジェクトの出発点は、サブ100psのタイミング分解能を維持しながら、同時に、550nmより長い波長で高いPDE を持つデバイス構造を開発することであった。この問題を解決する簡単なアプローチは、デバイス活性層の全厚みを増大させることである。特に、空間電荷領域または下部中性領域の厚みは増大させることが可能である。後者は、確かに、デバイス内の電場プロファイルに影響を与えることがなく、より厚いエピタキシャル層からプロセスを開始するだけで良いため、技術的観点から実行が容易なソリューションである。しかし、このアプローチにはいくつかの欠点も存在する。中性領域の厚みを増大させると拡散テールの寿命が長くなり、その結果としてタイミング分解能が悪化する。

図2 プレーナSPAD(赤色線)の波長依存光子検出効率(PDE)(a)が「厚い」リーチスルー構造(緑色線)と30psのタイミング解像度を持つ「薄い」初期プレーナ構造(青色線)のPDEと比較されている。タイミング解像度(b)も3つの異なる構造に対して比較されている(3)。

(もっと読む場合は出典元へ)

出典元

https://ex-press.jp/wp-content/uploads/2012/01/201201_0026feature02.pdf