厳しい偏波試験を要求するコヒーレント通信システム

すべての偏波関連機能を評価する試験方法と関連機器は、様々なユーザにとってコヒーレントトランシーバとシステムの定量的評価に役立つ。

光ネットワーク開発における最近の関心は、時代に合わなくなった10Gbpsネットワークの伝送距離とデータ容量をコスト効率良く増強する方法に集っている。コヒーレント検出と偏波分割多重は、40~100Gbpsネットワークを実現するキーテクノロジとして登場した。この組合せは、チャンネルのスペクトル効率を大幅に向上させ、各チャンネルの比較的狭い光帯域幅による高ビットレート伝送を可能にする。今や、40、100、または160Gbpsチャンネルさえもが、既存のチャンネル間隔50GHzの10Gbps波長分割多重(WDM)の基盤インフラを使って伝送されている。

偏波分割多重(PDM)は、同一ビットレートの二つの偏波チャンネルを同一波長チャンネルへと一体化させてスペクトル効率を 2倍にする。コヒーレント検出は、最先端変調方式を使って多準位の位相と低レートの振幅変調を同一波長チャンネル上に多重化することを可能にする。例えば、四位相偏移変調(QPSK)とPDMを使うと、10Gbps直接チャンネルの帯域幅内で40Gbps伝送が可能になる。偏波モード分散(PMD)と波長分散(CD)による劣化効果は整合的に低減される。

コヒーレント検出は信号の位相、振幅、偏波情報を保持しているため、このようなシステムは、高速デジタル信号処理(DSP)回路とアルゴリズムを使って電気ドメインで偏波分割多重を処理することができる。CD補償、PMD補償(PMDC)、偏波依存性損失補償(PDLC)などの重要なシステム障害の補正機能も電気的に処理可能である。ただし、システム性能の検証は常に必要である。

システム性能の検証

トランシーバの開発者の場合、開発を成功させるには各種DSP回路とアルゴリズムの性能評価が必要になる。トランシーバ市場のシステムインテグレータの場合、様々なベンダからのトランシーバの性能を比較することが重要になる。そして、ネットワークオペレータの場合、様々なベンダのシステムの性能評価と比較を行うことによって、オペレータは合理的な購買決定ができるようになる。これらの例のすべてにおいて、評価は三つの主要な偏波関連機能、つまり偏波多重分離、PMDC、PDLCについて実施する必要がある。

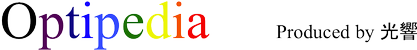

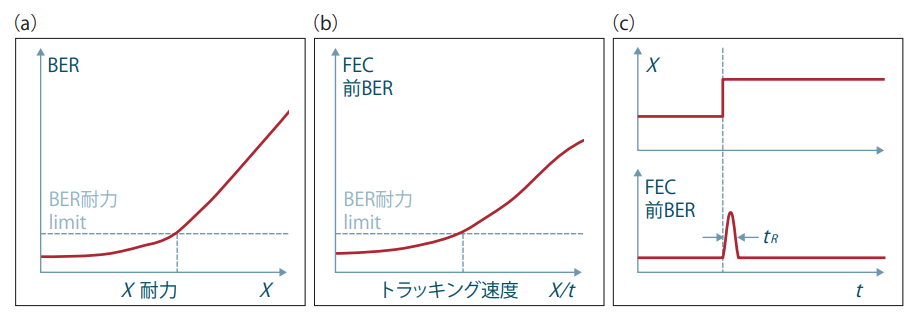

コヒーレント検出システムに対しては、一般的なセットアップがすべての偏波関連機能の性能を試験できるように開発されている(図1)。偏波インペアメント(機能障害)は時間とともに急速に変化するため、関連機能は偏波状態(SOP)、PMD、PDLなどの各種偏波パラメータの変位に対して試験する必要があることに注意すべきである。これらのパラメータを適切に試験するには、コヒーレント検出システムにおける各種偏波関連性能試験の定義を理解しておくことが重要である。これらの評価試験は三つの基本タイプ(耐力範囲、トラッキング速度、回復時間)について実施される(図2)。性能指標としてはシステムのビット誤り率(BER)が使用されているが、アイダイヤグラムまたはパワーペナルティにおける開口サイズなどの他のパラメータも候補になる。

耐力範囲試験は、信号の品質が許容レベルを越えて劣化する前に、システム中に存在する試験下のインペアメント(PMDまたはPDL)の最大量を決定する。これらのインペアメントが増加すると、それとともにBERも増加する。最大許容BERに対応するPMDまたはPDLがシステムの耐力範囲になる。

CDや信号対雑音(SN)比とは異なり、SOP、PMD、PDLはすべて実際の光ファイバ通信システムにおいて時間とともに急速に変化する。トラッキング速度試験は、評価されている回路/アルゴリズムがもはや変位に従わなくなり、信号品質が一定の準位を越えて劣化を起こす前に、試験下のパラメータがいかに急速に変化し得るかを決定する。順方向誤り訂正(FEC)前のBERを性能指標として使用したトラッキング速度試験では、試験下の回路/アルゴリズムのトラッキング速度は最大許容BERに対応する試験下のパラメータ(SOP、PMD、PDL)の変位速度である。

SOP、PMD、またはPDLの急な変化は試験下の回路/アルゴリズムにそれらを一時的に見失わせ、BERの過渡的増加の原因になる。回復時間試験は、試験下の回路/アルゴリズムがいかに迅速にその変化から回復し、BERを許容レベルまで復元できるかを決定する。特に、SOP、PMD、またはPDLの回復時間は、これら三つの各パラメータの破壊的ジャンプによって引き起こされた異常なレベルから、DSPがBERを復元するために必要な時間tRと定義される。

図1 コヒーレント受信器は一般に偏波多重分離、PMD補償、PDL補償機能用の三つの偏波関連回路/アルゴリズムを備えている。これら3タイプのエミュレーション機器は、PMD / PDL耐力範囲、SOP、PMDまたはPDLの変位に応答するトラッキング速度、これらのパラメータの急な変化への応答に必要な回復時間を含む。これらの機能を完全に評価するための各種偏波パラメータを発生させなければならない。

図2 偏波関連性能試験(XはSOP、PMD、またはPDL)は、( a)PMDまたはPDL耐力範囲試験、(b)SOP、PMD、またはPDLトラッキング速度試験(横軸はこれら三つのパラメータの変化速度)、( c)回復時間試験を含む。ここで、cの上部グラフはこれらのパラメータの急激な変化を表し、下部グラフは上部グラフで示されたステップ変化後にDSP回路がBERの制御を回復するために必要な時間を示す。

(もっと読む場合は出典元へ)

出典元

https://ex-press.jp/wp-content/uploads/2011/06/1106feature05.pdf