ビット当たりサブピコジュールのCMOSシリコンフォトニック受信機

ハイブリッド集積全CMOS光受信機は将来のチップ間とチップ内のインターコネクションに向けて大きく進歩している。

高性能デジタルコンピュータシステムは速度と容量の拡大が続き、ごく最近では処理コア数も増加している。さらなる拡大には高密度で広帯域の大規模インターコネクションばかりでなく、パッケージとシステムの両方のコスト効果の高い熱除去を実現する難しさを克服する超高効率通信リンクも必要になる(1)。その結果、将来のシステムにはサブピコジュール/ビットの通信リンクが必要になる。シリコン(Si)フォトニクスデバイスの独自な利点を利用すると、チップ内とチップ間の用途に有望な解決策としてのフォトニックインターコネクトが可能になる。しかしながら、超低パワーの端末間Siフォトニッ

クリンクは未だに実証されていない。

エネルギー効率に優れた光受信機は低パワーフォトニックリンクの重要なビルディングブロックの一つになる(p.35の「低パワー光受信機に関する従来の研究」を参照)。低パワー光受信機は三つの中核部品、すなわち、高い感度と低い寄生効果(回路設計に及ぼす意図しない静電容量や抵抗の影響)をもつ高速光検出器、パワー効率のよい大規模集積(VLSI)受信機回路および低い寄生効果をもつ集積部品が必要になる。

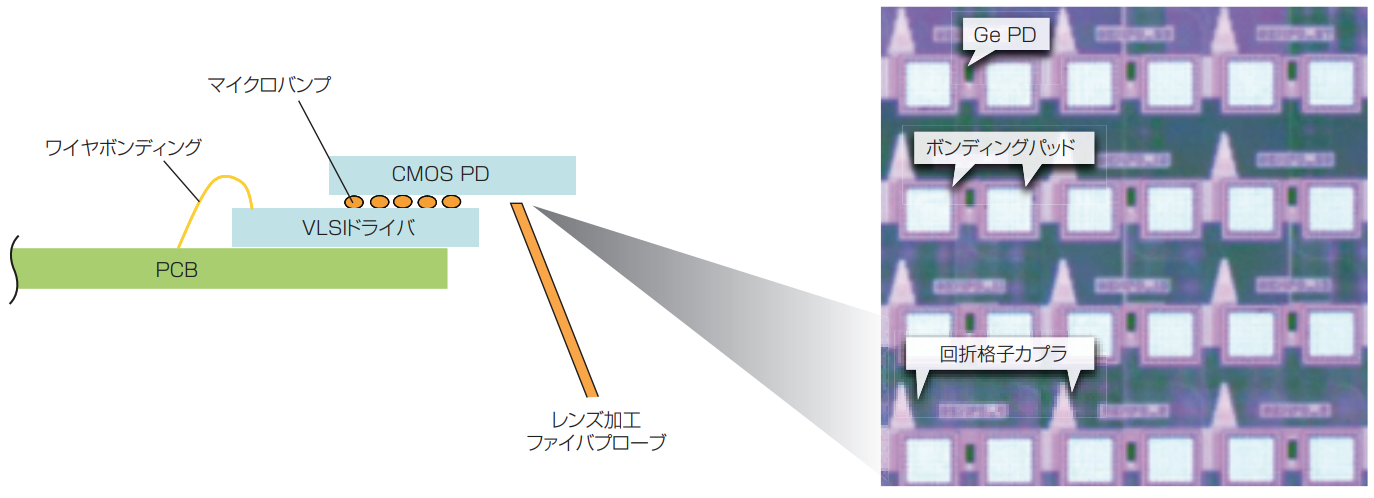

われわれはピコジュール/ビット受信機の障壁を破るために、これら三つのすべてを改善した。基板とその他のパラメータの要求とは異なるため、われわれは二つの異なるプラットホームを使用して導波路光検出器および関連するCMOS受信機回路を作製した。特殊な低寄生微小はんだ技術を用いてフォトニックデバイスとCMOS回路チップを集積し、ハイブリッド「CMOSフォトニックブリッジ」を形成した。この配置は局所通信のための電気インタフェースともう一つのチップとのグローバル配線をファイバまたは導波路を通して行う光アクセス機能を備えている。

CMOS Ge導波路光検出器

われわれはゲルマニウム(Ge)オンSiの単一ステップ低温成長を用いて、エバネセント結合によるGe p-i-n 導波路ダイオードを開発した(5)。このフォトダイオード導波路には光入力用の回折格子を集積した(図1)。その作製には米ラクステラ社(Luxtera)のGe適用オプトエレクトロニクス技術と米フリースケール社(Freescale)のHIP7 Siオンインシュレータ(SOI)130nm CMOSノードを組合せて使用した。このGe検出器は非常に小型で、約1.5×15μmのサイズを持つ。特性評価では、1550nmにおける0.7A/Wの高い感度、25℃における3μAの低い暗電流、そして0.5Vの逆バイアスを持つことが示された。1Vの逆バイアスでは、検出器には20fF以下の非常に低い静電容量と10GHz以上のー3dB 帯域幅が得られた。このGe-PIN 導波路検出器の優れた品質を利用すると、高い感度を持つ高速受信機の設計が可能になる。

図1 フリップチップ集積チップオンボード方式の回折格子カプラ付きSiフォトニック全CMOS Ge導波路光検出器を示している。(資料提供:サン/ラクステラ社)

CMOS VLSI受信機チップ

光受信機は変調された光倍号から電気デジタル信号への変換を行うが、そこでは前面にある光検出器が光信号を光電流として受信する。標準的なトランスインピーダンスアンプ(TIA) は、まず光電流信号を電圧に変換し、次に多重制限増幅器を用いて電圧信号をさらに増幅し、下流のデジタル回路による「1」または「O」の二値論理の識別を可能にする。優れたエネルギー効率を確保するために、われわれは三段TIA方式による低パワー受侶機の設計を採用し、その後段にはクロック検出増幅器を配置した(6) 。三段TIAからは約1×1がの全体利得が生成され、1OμA の入力信号に対して1OOmV の出力電圧が得られた。また、検出器と回路の両方からの残留熱雑音と検出増幅器内部のトランジスタ不整合に対して十分な信号対雑音比も得られた。三段TIAの後段に配置した簡単でパワー効率のよいクロック検出増幅器を用いてTIA出力の増幅を行い、フルスイングレベルのCMOS信号が得られるようにした。算出した入力参照雑音電流は1.1 μA であった。従来の光受侶機はアナログフィルタによるフィードバックを用いてTIAバイアスを制御し、適切な値を設定するが、この方法は信号パワーの消費が大きい。また、DC 平衡データが必要になり、余分の大きなエネルギーのオーバヘッドがリンク全体のパワー消費に付加され、8B/10B DC 平衡符号化では25%の追加になる。このオーバヘッドを最小にするために、われわれは大域同期リフレッシュ動作に基づくデジタルフィードバック方式を採用してTIAバイアスを正確に設定した(6) 。また、TIAバイアスを周期的にリフレッシュして周囲の環境変化と部品の経年変化から生じる信号パワーの変動を克服し、DC平衡データの伝送を不要にした。その結果、リフレッシュオーバヘッドは1%以下に減少したと推定される。

(もっと読む場合は出典元へ)

出典元

https://ex-press.jp/wp-content/uploads/2011/01/7f5786abd6002ff79fd2d349b9af9170.pdf