高いフレーム速度で動作する単一光子計数カメラ

32X32画素構成の単一光子計数カメラは、それぞれの画素の内部にすべての電子回路を内蔵したアバランシェダイオードから構成されている。このカメラは毎秒10万フレームの速度で動作する。

単一光子アバランシェダイオード(SPAD) は、レーザレーダ、蛍光相関分光法、蛍光寿命イメージング、粒度測定などの用途に使われる。最近までのSPADは点検出器または画素数に制約のあるアレイ検出器に限られていた。単点検出器の1例にはイタリアのマイクロフォトンデバイス社(Micro Photon Devices) が製造する光子計数検出器がある(www.laserfocusworld.com/articles/226763を参照)。この光子計数検出器は特注のシリコンプロセスを使用して、毎秒10以下の暗計数と30ピコ秒(ps) のタイミング分解能を実現している。また、SPADの製造プロセスを最適化して最高の光学的スループットを実現し、SPADの消滅回路とタイミング回路をデバイス本体から分離して、このような性能レベルを可能にしている。

最高の検出効率、最低の暗計数(LFWJ 2008年10月号p.52またはwww.laserfocusworld.com/ articles/335986を参照)および最速の分解能が必要になる用途では、このような点検出器が優れている。光学的に最適化されたSPADを構成し、電子回路を分離するアプローチは多点アレイ検出器にも拡張できるが、拡張可能な画素数には限界がある。電子回路を分離してそれぞれの画素を個別にアドレス可能にする方法は8素子モジュールに応用され、60素子にも適用された(1) 、(2) 。しかしながら、電子回路を画素から分離するには、複雑な半導体プロセスを使用した接続が必要になるため、このアプローチを数百個の画素に対して拡張することは難しく、実際には不可能だ。

32X32画素の光子計数カメラ

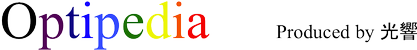

イタリアのミラノ工科大学SPADラボ(SPADlab, Politecnico di Milano) の研究グループは、すべての電子回路と計数器をそれぞれの画素に内蔵した32X32画素の単一光子計数アレイを開発した(図1) 。それぞれの画素のサイズは1OOx1OOμmであり、画素のピッチ(画素間の距離)はlOOμmになる。SPADとすべての電子回路は複雑な電子回路とSPADを同時に加工できる標準の高圧CMOSプロセスを使用して作製された。

使用時のアレイは、画素が光子を検出すると、アバランシェ電流が発生し、画素の可変負荷消滅回路(VLQC) がアバランシェ電流の検出、消滅およびSPADのリセットを行って、次の光子の検出を可能にする。一つのアバランシェ効果が終わると、クエンチング回路からの出カパルスが計数器へ送られる。計数器はデジタル回路から構成され、ユーザが選択したフレーム時間スロットのなかで検出された光子の計数と暗計数を行う。それぞれのフレームの最後に行われる動作では、ストップパルスがアレイの大域電子回路から送られる。この電子回路は、まず計数器が記録した事象数をストレージレジスタにいったん蓄積し、次にスタートパルスを発生して計数器をリセットする。その結果、新しいフレームのスタートが可能になる。

図1 32×32光子計数カメラの配置にはSPADを起動すると、VLQCがアバランシェ電流を検出し、回路を消滅し、SPADをリセットする(右)。計数データは補助回路から計数器へ送られる。(資料提供:ミラノ工科大学)

アレイのアーキテクチャ

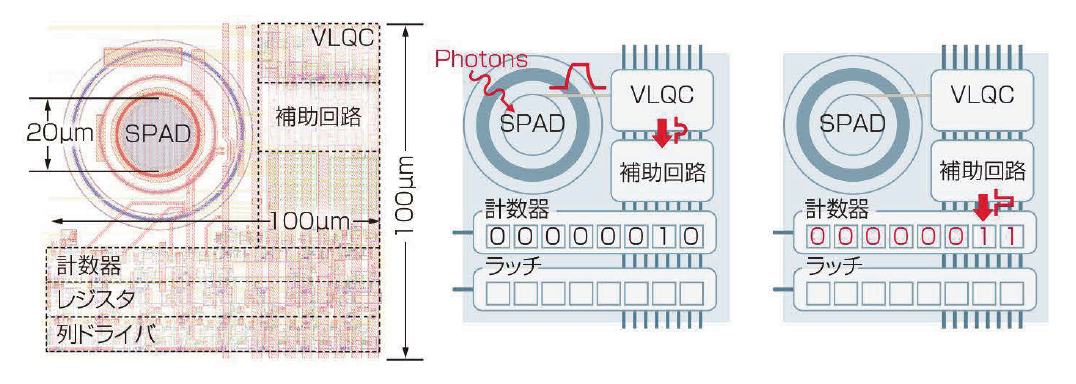

32X32光子計数カメラのアーキテクチャは完全な並列動作機能を持つ(図2) 。それぞれのフレームはストップ信号とその後のスタート信号がすべての画素に同時に流れて開始される。画素はそれぞれのフレーム時間内に入射する光子の検出と計数を行い、同時に、ストレージレジスタにはその前のフレームのときに累積されたデータが保持されている。その結果、データは読取られ、その時点のフレームのデータはアレイにより捕捉される。実現可能な最大のフレーム速度はアレイからのすべてのデータの読取りに必要な時間による制約を受ける。100MHzのシステム同期信号を使うと、それぞれの画素のデータを10ナノ秒で読取ることができる。したがって、32X32画素アレイの最大フレーム継続時間は、約10万フレーム/秒の連続フレーム速度に相当する10.25マイクロ秒になる。また、オンチップ大域電子回路からは撮像の柔軟性が得られ、ユーザはアレイから所望のすべてのサブ領域を選択できるため、全体のフレーム速度の増加が可能になる。例えば、1Ox1O画素の領域を選択すると、フレーム速度の最大値は102万4000フレーム/秒になる。

図2 イメージャの標準的なアーキテクチャを最も重要な入力/出カパッドとともに示している。この図は8X8アレイを例にして簡素化している。(資料提供ミラノ工科大学)

(もっと読む場合は出典元へ)

出典元

https://ex-press.jp/wp-content/uploads/2009/08/200908_ft03.pdf